CPU|SV|UVM|Verdi|答疑学习笔记|干货满满

1.前言

本文全部来自群内网友的智慧,我只是做一些整理的工作。以免高质量的内容被埋没,同时也希望这些好东西可以帮助到更多的朋友。

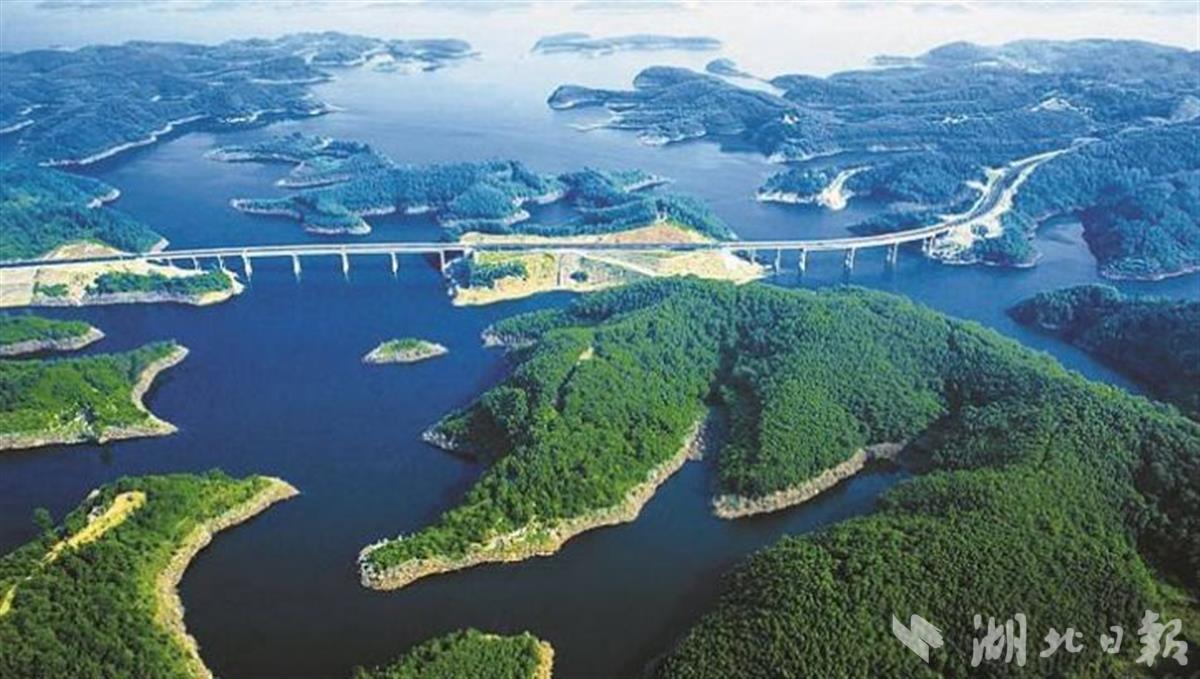

(资料图片仅供参考)

(资料图片仅供参考)

2.分享一些高质量的CPU书籍

3.分享verilog书籍/SV经典文章/重构改善既有代码设计

4.下面的语法什么意思

rx_data位宽固定是128,bist_wdata位宽参数化

[m +:n]的含义是:从bit[m]位置向上取n bit;

[m -:n]的含义是:对应的从bit m向下取n bit。

5. 网友整理的SV和verilog学习笔记

6. Genus中的一个bug

下图中第65行的”==”应该写成”===”,详细的原因,请参考本公众号的文章:

verilog中==/!=和===/!==的区别

7. pack_bytes和unpack_bytes的含义和用法

8.保存仿真过程中的mem和数据

Q:请问大家有没有什么办法可以将仿真过程中某个时刻的所有寄存器还有memory的数值全部保存下来,下次开始仿真用这些数值作为初始值?

A: Verdi nwave窗口选中信号file-report selected signals设置下文件名option -of b/h/d -period采样时间,出来的.txt在tb内$readmem就行了。保存的时刻是两个marker的位置。那个尝试了,report生成的中信号名称不全,而且如果说设计很大,寄存器数量太多重新加载也不好对应的readmem。Verdi有这个功能,apps。

9. svt_mem使用的问题

A:你加个set_addr_range在顶层ENV里面连接,然后通过config_db_set;然后在自己的组件里面get_mem就可以使用了。

10. 以svt_apb为例,跑一个svt_vip的example

example.svt如下图所示,svt支持的所有的example都在这里了

11. verdi的marker操作

ctrl+m增加marker,shift+m管理marker.

12. coverage的ccf文件怎么使用

-coverage all -coverfile /xx/yy/zz/xyz/config.ccf

13. 关于vertual sequencer和sequencer使用的问题

Q:请教各位,有个现象:我在seq里declare_p_sequencer为vir_seqr,接下来body里做了赋值cfg = p_sequencer.cfg;如果在test里挂载到vir_seqr,就是对的。但如果挂载到vir_seqr的子一级seqr,就报赋值语句错。如果vseqr里定义多个seqr,那必须向下挂载,该怎么办呢?我现在就是env里声明vseqr,在vseqr里有seqr及cfg,然后就到test里seq.start(env.vseqr.seqr);感觉这样会把seqr当做p_sequencer,所以报错。但不知道多个seqr时怎么写start,或者什么结构。

A: virtual sqr相当于一个梳理器 把需要的seqr的句柄都放进去,然后你的seq需要用哪个seqr方便指向,virtual seq里面的子seq如果在不同的sqr上 做好对应关系,可以直接把virtual seq挂在virtual sqr上。挂载到ver_seqr.seqr上,此时的m_sequencer是seqr,所以p_sequencer应该也是seqr,非vseqr。对,如果p_sequencer的挂载不一致,就报cast错误。

14. PCIE6.0计划

15. uvm_config_db

16. linux删除文件夹A中除了run和后缀.sv、.f的所有文件和目录

转自芯片验证日记,感谢关注。

关键词: